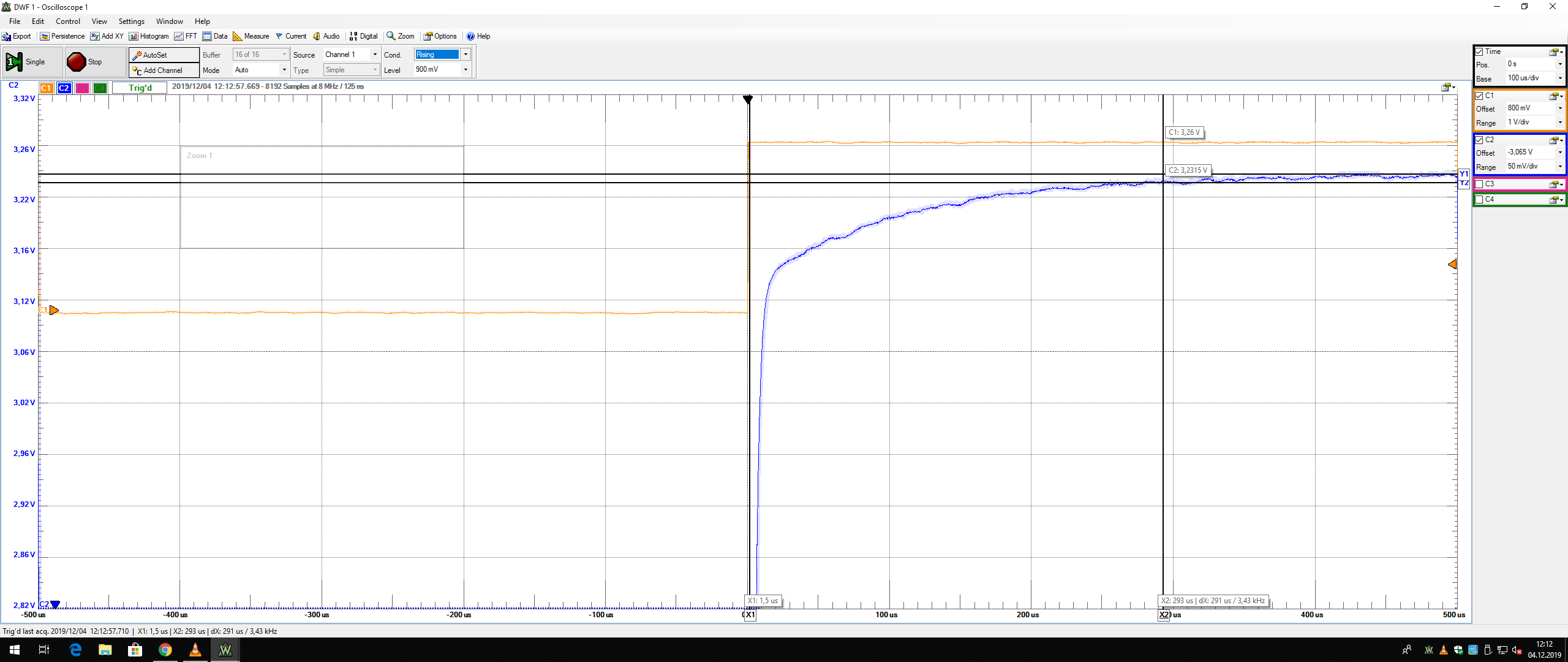

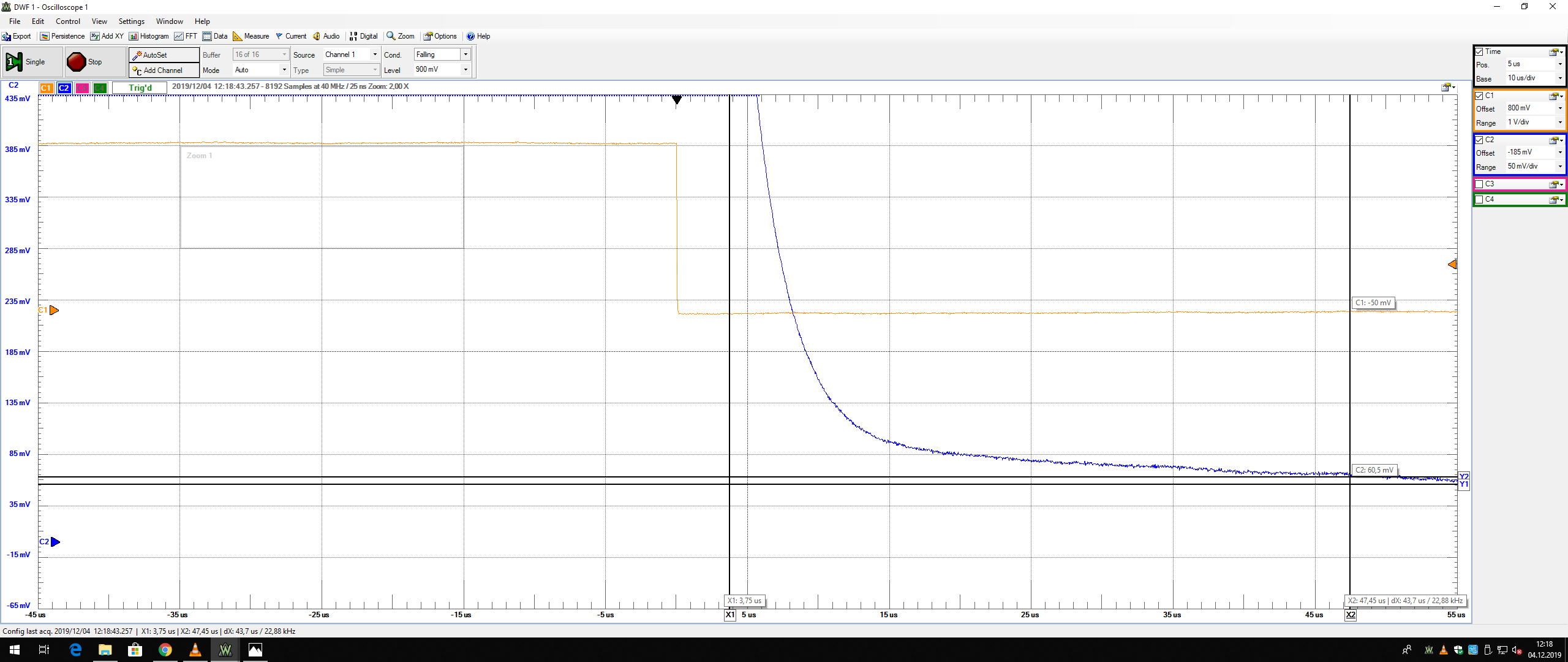

8-bit DAC Measurment

|

|

|

Interface ElectronicsLaboratory 04: 8-bit R2R DAC (11.12.2019)Group D ***877, ***953 |

|

|

|

|

|

|

|

|

LTSPICE INL, DNL FFT Analysis |

|

Generate a calibration lookup table with ramp measurement

CONCLUSION

Hochschule für angewandte Wissenschaften Kempten, Jörg Vollrath, Bahnhofstraße 61 · 87435 Kempten Tel. 0831/25 23-0 · Fax 0831/25 23-104 · E-Mail: joerg.vollrath(at)fh-kempten.de Impressum

|